November 13–14, 2024 | Online

## Integrated Development Workflow for 5G Applications Using AMD Versal<sup>™</sup> Adaptive SoC

Rob Graessle, AMD

Noam Levine, MathWorks

MATLAB **EXPO**

## Agenda

- Workflow Overview

- AMD Versal Adaptive SoCs and AMD Vitis<sup>™</sup> Model Composer

- Connecting HDL Coder from MathWorks to AMD Vitis Model Composer

## Workflow Overview

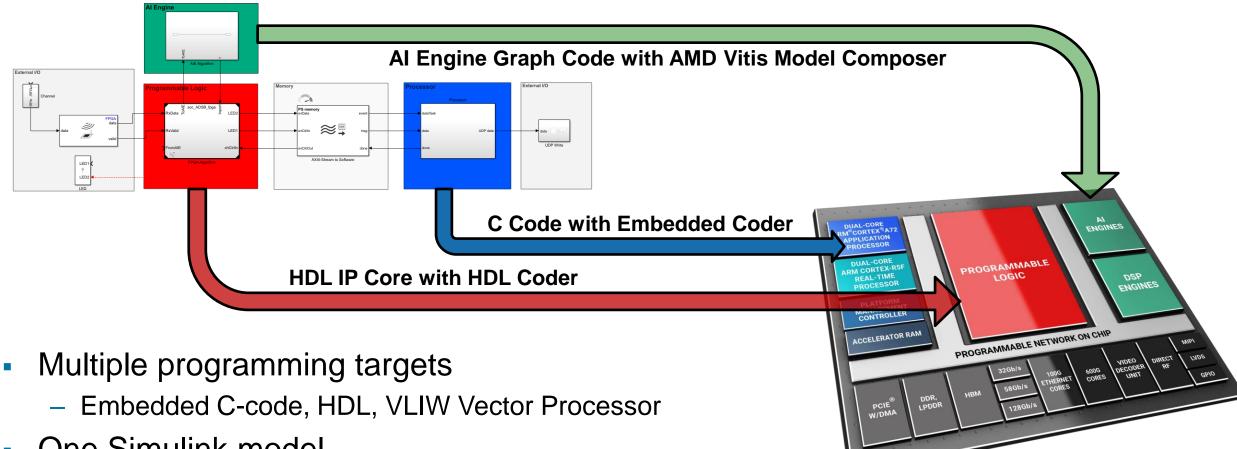

Targeting all Versal Programmable Engines from MATLAB and Simulink

MATLAB EXPO

- One Simulink model

- Unified design and simulation environment

AMD Versal Adaptive SoCs and AMD Vitis Model Composer

| AMDA<br>VERSAL |                             | AMDZ<br>Versal | AMD<br>VERSAL<br>Premium          | AMD<br>VERSAL<br>Prime               |

|----------------|-----------------------------|----------------|-----------------------------------|--------------------------------------|

| 5G Beamforming | Al-Enabled<br>Stereo Camera | SK Camera      | <section-header></section-header> | Satellite-Based<br>Internet Services |

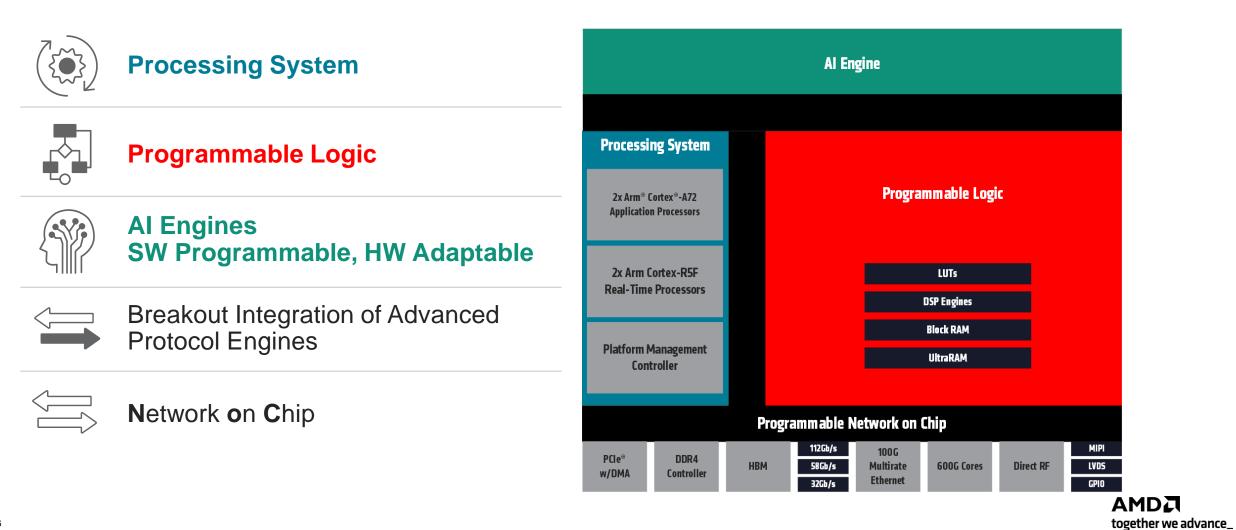

## **AMD Versal<sup>™</sup> Adaptive System-on-Chip**

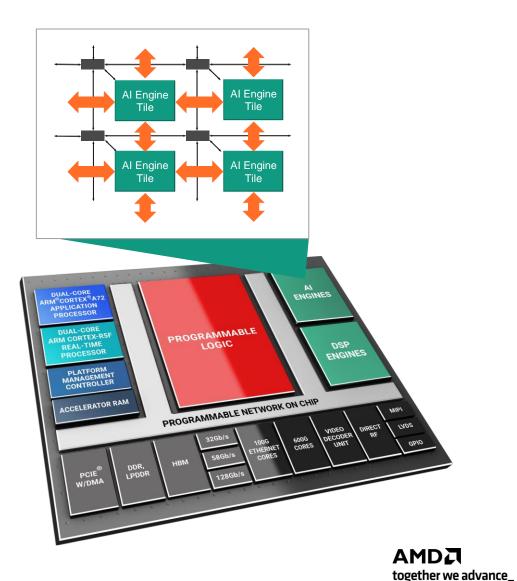

## Introduction to AMD Versal<sup>™</sup> AI Engine

First introduced in AMD Versal<sup>™</sup> AI Core Series

Software programmable

- VLIW processor running at 1 GHz+

- Massively reduce development time vs traditional RTL

Array of vector processors running at 1 GHz+

- From 8 tiles on the smallest device (VE2002)

- Up to 472 tiles on the largest device (VP2802)

Terabytes/sec of interface bandwidth

• Direct, massive throughput to adaptable hardware engines

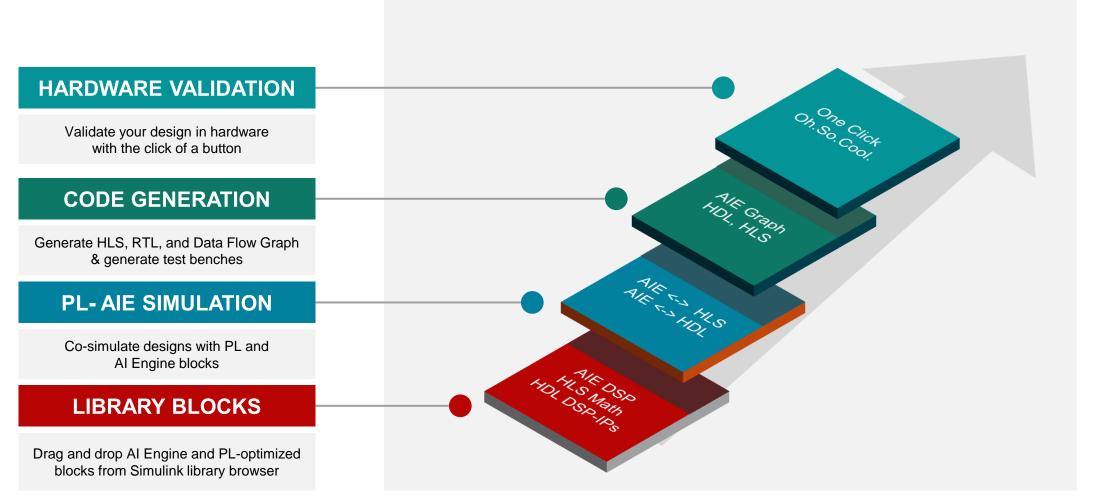

## **Integrated Workflow for AI Engine Development**

AMD Vitis Model Composer accelerates Versal development by offering a productive environment within MathWorks Simulink® for simulation, code generation, and hardware validation.

## **AMD Vitis™ Model Composer At A Glance**

[Public]

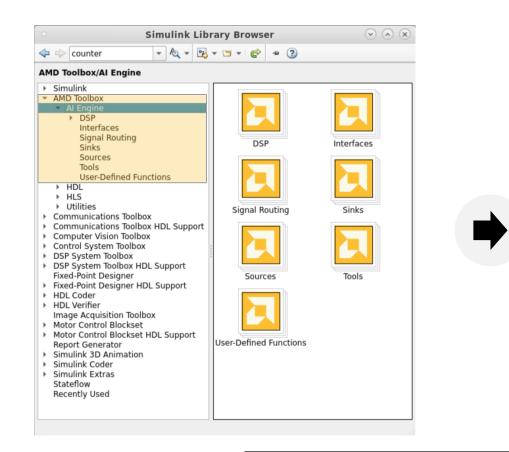

## **AI Engine Library Blocks**

#### AI Engine->DSP->Stream I/O blocks DDS Stream out[0] DFT Stream out[ FFT Dynamic Point Stream out[] DDS Stream DFT Stream FFT Dynamic Point Stream in[0] FIR Asymmetric Stream out[0] in[0] FIR Asymmetric Decimation Stream out[0] FFT Stream out[1] FFT Stream FIR Asymmetric Decimation Stream FIR Asymmetric Stream in[0] FIR Halfband Interpolator Stream out[0] in[0] FIR Interpolation Stream out[0] FIR Halfband Decimator Stream out[0] FIR Halfband Decimator Stream FIR Halfband Interpolator Stream FIR Interpolation Stream 1[0] FIR Resampler Filter Stream out[0] in[0] FIR Symmetric Decimation Stream out[0] in[0] FIR Symmetric Stream out[0] FIR Resampler Filter Stream FIR Symmetric Decimation Stream FIR Symmetric Stream out[0 out[ [0] IDFT Stream out[0 IFFT Stream Mixed-Radix FFT Stream out[1] out[1] IDFT Stream IFFT Stream Mixed-Radix FFT Stream outf Mixed-Radix IFFT Stream 1[0] Mixer Stream outf0 Vectorized Sample Delay Stream out SampleDelay Mixed-Radix IFFT Stream Mixer Stream Vectorized Sample Delay Stream outf0 Window Function Stream

out[1]

Window Function Stream

Bit accurate

AIE and AIE-ML devices

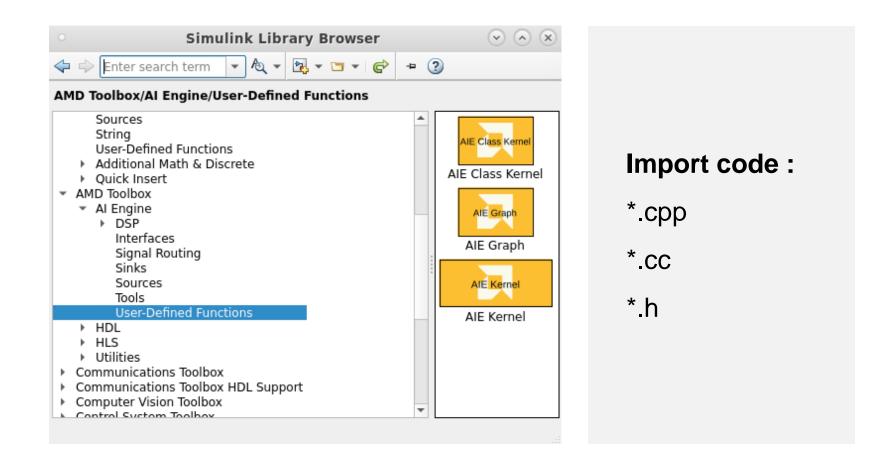

## Import Custom AI Engine Code as a Block

...and connect to other blocks

#### [Public]

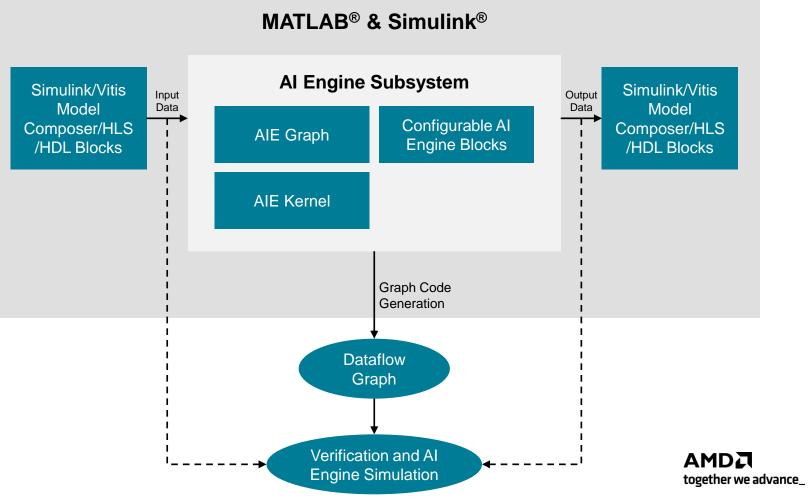

## **AMD Vitis™ Model Composer for AIE Development**

AMD Vitis<sup>™</sup> Model Composer is a model-based design tool that enables rapid design exploration within the MathWorks MATLAB<sup>®</sup> and Simulink<sup>®</sup> environment.

Advantages for AIE-DSP Design Flow:

- Automatically generate Graph C Code for AI Engines

- Import HDL blocks in AIE designs

- Heterogeneous simulation with robust test bench capabilities from Simulink<sup>®</sup>

## Connecting HDL Coder from MathWorks to AMD Vitis Model Composer

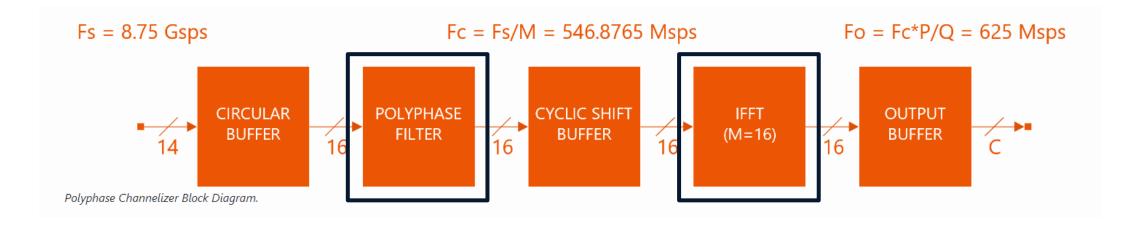

## **Example – Polyphase Channelizer**

From <a href="https://github.com/Xilinx/Vitis\_Model\_Composer/tree/2024.1/Examples/AIENGINE\_plus\_PL/AIE\_HLS/Channelizer">https://github.com/Xilinx/Vitis\_Model\_Composer/tree/2024.1/Examples/AIENGINE\_plus\_PL/AIE\_HLS/Channelizer</a>

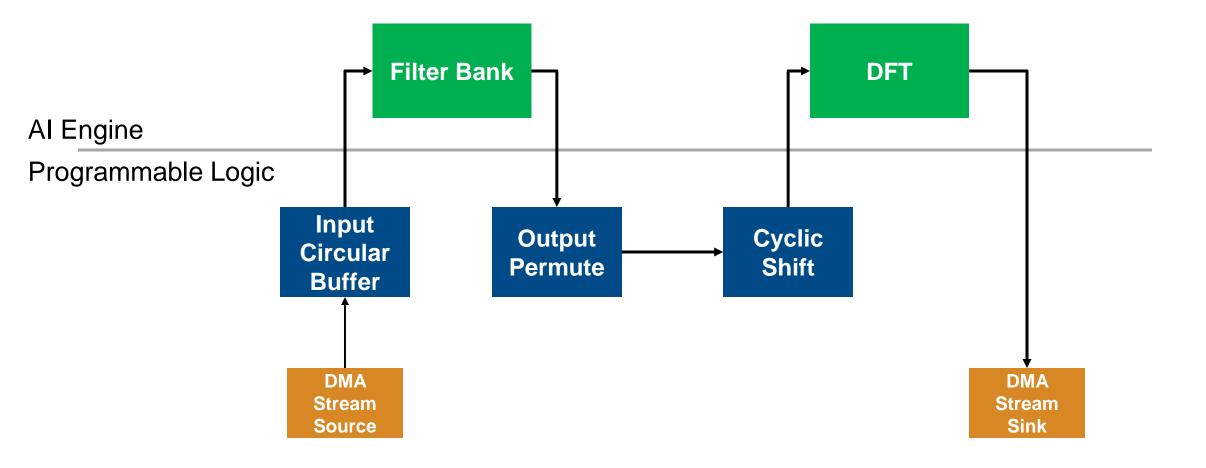

## System Partitioning

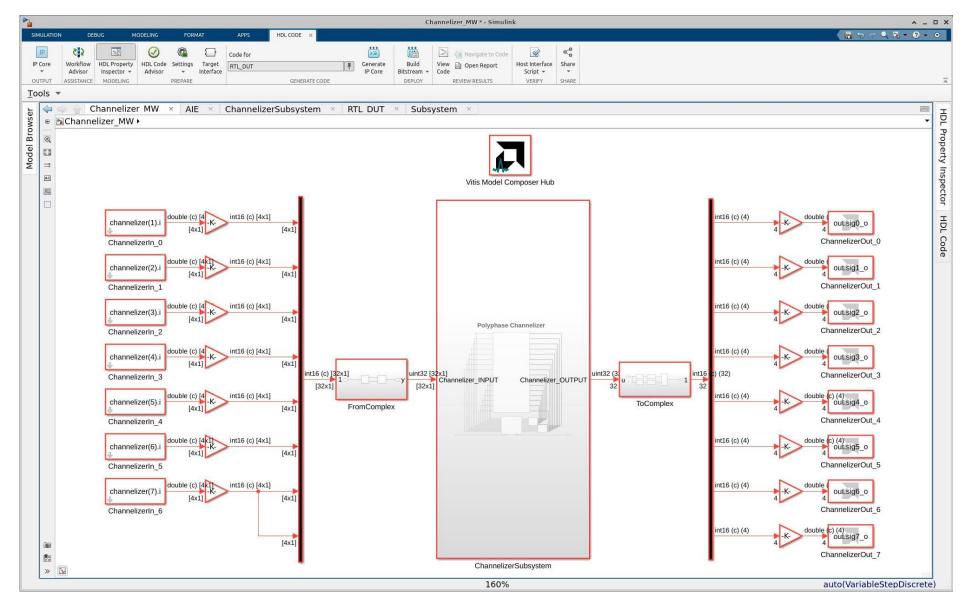

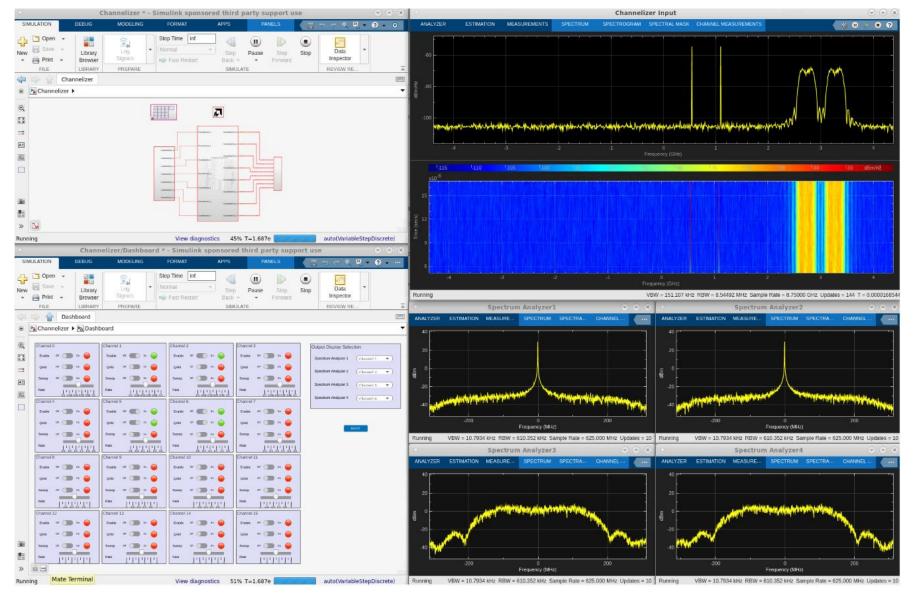

## **Top-Level Simulink Implementation**

MATLAB **EXPO**

17

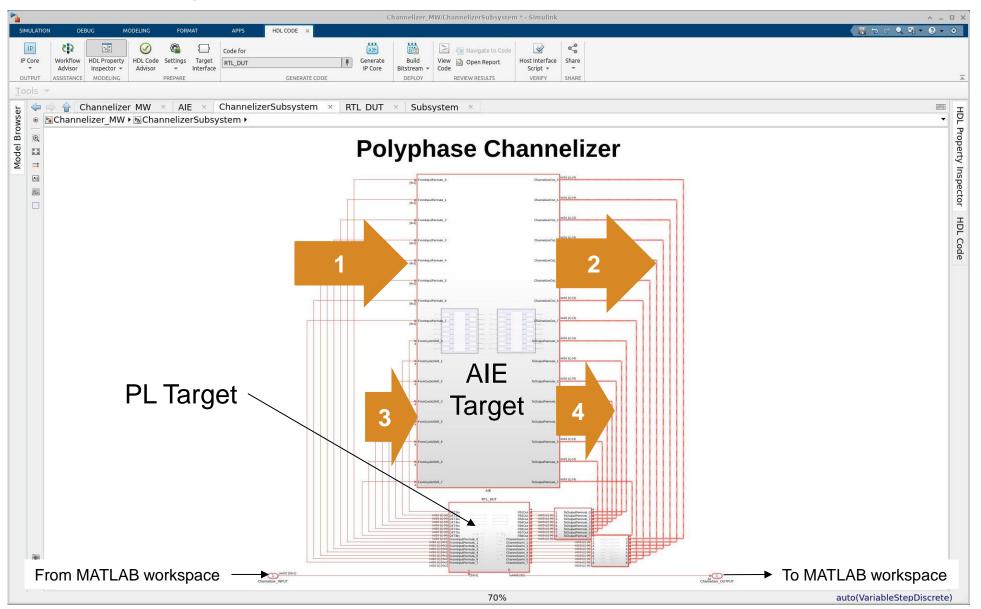

## **Simulink Implementation**

#### MATLAB EXPO

### **Model Simulation**

MATLAB **Expo**

19

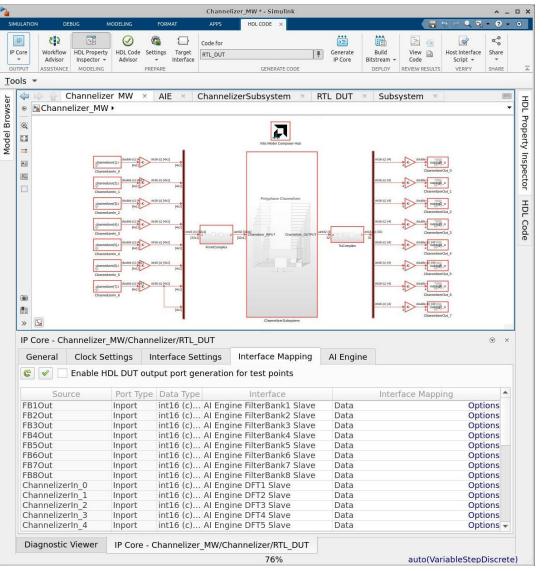

## **Environment Setup for Deployment**

- Define I/O ports for blocks targeted to Programmable Logic and AI Engine

- Blocks targeted to Programmable Logic will go through HDL Coder

- Blocks targeted to AI Engines will go through AMD Vitis Model Composer

New Workflow Access from the Simulink Desktop

Access to HDL Coder workflows now available in the Simulink Toolstrip

| Channelizer_MW/ChannelizerSubsystem * - Simulink            |             |                                                     |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ^ _ O X               |

|-------------------------------------------------------------|-------------|-----------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| SIMULAT                                                     | ION DEBUG M | IODELING FORMAT                                     | APPS HDL CODE X                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ○ • ? •               |

| IP Core<br>OUTPUT<br>Tools                                  |             | HDL Code Settings<br>Advisor - Interface<br>PREPARE | Code for<br>RTL_DUT<br>GENERATE CODE | Image: State of Code Image: State of Code Image: State of Code   Build View Open Report Host Interface   Bitstream v Code Open Report Share   EMBEDDED SYSTEM INTEGRATION Image: State of Code Image: State of Code   Image: State of Code Image: State of Code Image: State of Code   Image: State of Code Image: State of Code Image: State of Code   Image: State of Code Image: State of Code Image: State of Code   Image: State of Code Image: State of Code Image: State of Code   Image: State of Code Image: State of Code Image: State of Code   Image: State of Code Image: State of Code Image: State of Code   Image: State of Code Image: State of Code Image: State of Code   Image: State of Code Image: State of Code Image: State of Code   Image: State of Code Image: State of Code Image: State of Code   Image: State of Code Image: State of Code Image: State of Code   Image: State of Code Image: State of Code Image: State of Code   Image: State of Code Image: State of Code Image: State of Code <td< td=""><td>*</td></td<> | *                     |

| v → → Channelizer MW × AIE × ChannelizerSubsystem × RTL DUT |             |                                                     |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ₩ F                   |

| Model Brows                                                 |             | ▶ ► ChannelizerSubsy                                | rstem >                              | Build Bitstream   Cenerate IP core, create IP core project, and build bitstream for   Selected system   DEPLOYMENT   Image: Program Target Device   Program Target FPGA device   SOFTWARE INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | JL Property Inspector |

|                                                             |             |                                                     |                                      | Software Interface Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | tor                   |

|                                                             |             |                                                     |                                      | Software Interface Model<br>Generate a software interface model with IP core driver blocks<br>for C/C++ code generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | HDL Code              |

## Summary

- AMD Versal Adaptive SoCs provide a heterogeneous compute environment combining processor cores and programmable logic with a powerful VLIW vector processing "AI Engine" to speed signal processing calculations

- Using HDL Coder from MathWorks with AMD Vitis Model Composer enables users to target all the programmable engines on Versal from a single Model-Based Design environment

## For More Information

- 1. Visit **MathWorks.com/AMD** for more information on targeting workflows for AMD Adaptive FPGAs and SoCs

- 2. Contact **fpga\_expert@mathworks.com** if you want to evaluate this workflow using HDL Coder with AMD Vitis Model Composer

# MATLAB EXPO

© 2024 The MathWorks, Inc. MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See *mathworks.com/trademarks* for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.